# Enhancing ON- and OFF-State Performance of Quasi-Vertical GaN Trench MOSFETs on Sapphire With Reduced Interface Charges and a Thick Bottom Dielectric

Renqiang Zhu<sup>®</sup>, *Graduate Student Member, IEEE*, Huaxing Jiang<sup>®</sup>, *Member, IEEE*, Chak Wah Tang, and Kei May Lau<sup>®</sup>, *Life Fellow, IEEE*

Abstract—In this letter, we report the enhancement of ON- and OFF-state performance in vertical GaN trench MOSFETs through fabrication process optimization. The ON-state device performance was effectively improved by reducing MOS channel interface charges with a piranha cleaning process prior to the gate dielectric deposition. For the OFF-state, the breakdown voltage ( $V_{BR}$ ) of the device was greatly enhanced via suppressing the electric field in the gate dielectric near the bottom of the gate trench with a thick bottom dielectric process. As a result, highperformance quasi-vertical GaN trench MOSFETs grown on sapphire substrates with a 4- $\mu$ m-thick drift layer are demonstrated, exhibiting a low specific ON-resistance of 0.95 m $\Omega$  · cm<sup>2</sup>, a high maximum drain current of 3.4 kA/cm<sup>2</sup>, a large threshold voltage of 6.1 V (defined at  $I_D$  of 1 A/cm<sup>2</sup>), and a high V<sub>BR</sub> of 485 V.

*Index Terms*—Gallium nitride, vertical trench MOSFET, interface charge, thick bottom dielectric, breakdown voltage.

## I. INTRODUCTION

**W** ERTICAL GaN-based transistors have shown enormous potential for efficient power switching applications due to their high voltage and high current handling capability. Progress has been made on developing vertical GaN transistors, including vertical GaN trench MOSFETs [1]–[7], the current aperture vertical electron transistors (CAVETs) [7]–[12] and vertical GaN fin MOSFETs [13]–[15]. Considering the high threshold voltage ( $V_{\text{th}}$ ) above 3 V preventing false turn-on and simple fabrication process (without regrowth step), vertical GaN trench MOSFET is a competitive candidate suitable for volume manufacturing. Lowering the channel resistancedependent  $R_{\text{ON}}$  is key to minimize the power loss. The existence of high-density positive channel interface charges [1]–[7] can lead to a reduced  $V_{\text{th}}$  [4] and poor channel mobility

Manuscript received December 11, 2021; revised January 12, 2022; accepted January 22, 2022. Date of publication January 25, 2022; date of current version February 24, 2022. This work was supported by the Research Grants Council of Hong Kong under General Research Fund Grant 16215818. The review of this letter was arranged by Editor T. Palacios. (*Corresponding authors: Huaxing Jiang; Kei May Lau.*)

The authors are with the Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong (e-mail: hjiangab@connect.ust.hk; eekmlau@ust.hk).

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2022.3146276.

Digital Object Identifier 10.1109/LED.2022.3146276

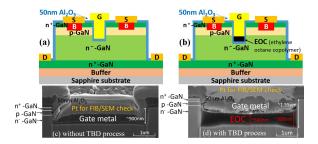

Fig. 1. Cross-sectional schematics of fabricated quasi-vertical GaN trench MOSFETs (a) without a thick bottom dielectric (TBD) process and (b) with a TBD process. "S", "D", "G", and "B" refers to "Source", "Drain", "Gate", and "Body", respectively. Cross-sectional SEM images of the gate trench region of devices (c) without TBD and (d) with TBD.

[16], [17]. Therefore, a proper cleaning process is necessary to improve channel property for better ON-state behavior. Piranha cleaning was found effective to improve the dielectric/GaN interface in planar GaN MOS capacitors on c-plane GaN surface [18], [19]. For the OFF-state performance, the reported device breakdown voltage  $(V_{BR})$  is far below the theoretical value of the non-punch-through GaN p-n junctions, which is mainly caused by the immature gate-to-drain breakdown due to the high peak electric field crowding at the trench bottom corner [1]–[4], [6], [7], [20], [21]. As such, suppressing the electric field at the gate trench corner is vital to enhance the device breakdown voltage. One effective solution was introducing a thick SiO<sub>2</sub> layer in the gate trench as the field oxide, as demonstrated in vertical GaN fin MOSFETs [13]–[15], similar to the thick bottom dielectric (TBD) reported in Si [22], [23] and SiC [24], [25] vertical MOSFETs. Effects of the TBD on the ON- and OFF-state performance in inversion-channel GaN trench MOSFETs have not been investigated.

In this work, we report significant enhancement of ON- and OFF-state performance of vertical GaN trench MOSFETs with reduced interface charges and a thick bottom dielectric. The demonstrated quasi-vertical GaN trench MOSFETs exhibit not only a large  $V_{\text{th}}$  of 6.1 V, but also a low specific ON-resistance  $(R_{\text{ON},\text{sp}})$  of 0.95 m $\Omega \cdot \text{cm}^2$  and a high maximum drain current  $(I_{\text{D,max}})$  of 3.4 kA/cm<sup>2</sup>, and a  $V_{\text{BR}}$  of 485 V.

# **II. DEVICE DESIGN AND FABRICATION**

The  $n^+$ -p- $n^-$ -n<sup>+</sup>-GaN structures for the quasi-vertical trench MOSFETs were grown on sapphire substrates by Metal Organic Chemical Vapor Deposition (MOCVD) (Fig. 1).

0741-3106 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information. The epilayers, from bottom to top, consist of a  $1-\mu m$  i-GaN buffer, a  $1-\mu m n^+$ -GaN [Si:  $5 \times 10^{18} \text{ cm}^{-3}$ ], a  $4-\mu m n^-$ -GaN drift layer [Si:  $3 \times 10^{16} \text{ cm}^{-3}$ ], a 400-nm p-GaN body [Mg:  $1.2 \times 10^{19} \text{ cm}^{-3}$ ], and a 200-nm n<sup>+</sup>-GaN layer [Si:  $5 \times 10^{18} \text{ cm}^{-3}$ ].

The vertical MOSFETs without TBD shared the same fabrication process as the work we have reported [4], except that two different channel cleaning processes were adopted before the gate dielectric (50-nm Al<sub>2</sub>O<sub>3</sub>) deposition: (I) buffered oxide etchant (BOE) for 2 min only; (II) piranha  $(H_2SO_4:H_2O_2 = 10:1, at 120^{\circ}C)$  for 10 min + BOE for 2 min. For the fabrication process of devices with TBD, compared with the ones without TBD: (1) a deeper trench of  $\sim 1.5 \ \mu m$ ( $\sim$ 900 nm for device without TBD) was etched; (2) before gate metal deposition, a layer of ethylene octene copolymer (EOC, from Everlight Chemical, with a dielectric constant of 3.6, a breakdown field of 4.1 MV/cm, and a glass transition temperature of 230°C) was blanketly coated to fill the gate trench, cured at 150°C for 30 min on a hotplate and etched back by  $O_2$  plasma, leaving around 500~600 nm EOC only in the gate trench to form the thick bottom dielectric. The cross-sectional schematic of the vertical MOSFETs without and with the TBD is shown in Fig. 1(a) and (b), respectively. After device fabrication, the corresponding gate stack of the device was characterized using scanning electron microscopy (SEM) as shown in Fig. 1(c) and (d). It can be observed that both devices exhibit near 90-degree vertical sidewalls of the gate trench, which has been reported vital for the carrier transport [6]. Moreover, for the device with TBD (Fig. 1(d)), the EOC near the gate trench sidewall was found thicker than that in the center region, which is in favor of reducing the electric field strength at the trench bottom corners.

The devices reported here feature a rectangular gate trench with a 4  $\mu$ m × 100  $\mu$ m area. The gate trench sidewalls were aligned to *m*-plane for better ON-state performance [6], [26]. The active area of the device for specific ON-resistance and current density normalization is regarded as (4  $\mu$ m trench length + 4  $\mu$ m drift region thickness) × (100  $\mu$ m trench width + 4  $\mu$ m drift region thickness) = 832  $\mu$ m<sup>2</sup>, taking the lateral current spreading length (4  $\mu$ m) in the drift region into account [4], [6]–[8]. The total device area is 200  $\mu$ m × 300  $\mu$ m, including the gate, source and drain contact pads.

#### **III. DEVICE RESULTS AND DISCUSSION**

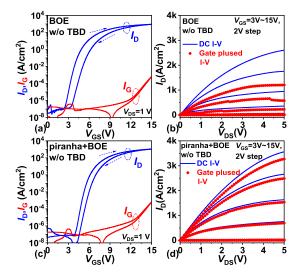

The device without additional piranha cleaning (without TBD) presents an ON/OFF current ratio  $(I_{ON}/I_{OFF})$  of  $\sim 1 \times 10^9$ , a gate current  $(I_G)$  of  $5.7 \times 10^{-4}$  A/cm<sup>2</sup> (at  $V_{GS}$ of 15 V), a  $V_{th}$  of 4.8 V (at  $I_D$  of 1 A/cm<sup>2</sup>), a  $V_{th}$  hysteresis (from  $I_D$ - $V_{GS}$  double sweep) of 1.3 V, a subthreshold slope (SS) of 281 mV/dec. In addition, a  $I_{D,max}$  of 2.61 kA/cm<sup>2</sup> and a  $R_{ON,sp}$  of 1.03 m $\Omega$ ·cm<sup>2</sup> are also demonstrated at  $V_{GS}$  of 15 V (Fig. 2(a) and (b)). The device made from the same epi with additional piranha cleaning (without TBD) shows a similar  $I_{ON}/I_{OFF}$  of  $\sim 1 \times 10^9$ , a similar  $I_G$  of 5.6  $\times 10^{-4}$  A/cm<sup>2</sup> (at  $V_{GS}$  of 15 V), an increased  $V_{th}$  of 6.2 V (at  $I_D$  of 1 A/cm<sup>2</sup>), a reduced  $V_{th}$  hysteresis of 0.8 V, a smaller SS of 228 mV/dec, a remarkably enhanced  $I_{D,max}$  of 3.56 kA/cm<sup>2</sup> and a reduced  $R_{ON,sp}$  of 0.85 m $\Omega \cdot cm^2$ , as shown in Fig. 2 (c) and (d).

The increase of  $V_{\rm th}$  (from 4.8 V to 6.2 V) indicates a reduction of fixed interface charges, from  $\sim 3.7 \times 10^{12}$  cm<sup>-2</sup> to  $\sim 2.5 \times 10^{12}$  cm<sup>-2</sup> with the employment of additional piranha cleaning, based on the extracted effective acceptor concentration ( $N_{\rm A}$ ) of  $\sim 1.6 \times 10^{18}$  cm<sup>-3</sup> in the p-GaN layer for both devices [4]. The reduced SS (281 mV/dec

Fig. 2. (a) Transfer and (b) output (DC & pulsed I-V) characteristics of vertical MOSFET (without TBD) without additional piranha cleaning; (c) transfer and (d) output (DC & pulsed I-V) characteristics of vertical MOSFET (without TBD) with additional piranha cleaning. For gate pulsed *I-V* measurement in both (b) and (d), quiescent gate bias is -20 V, the pulse width is 500  $\mu$ s, and the pulse period is 1 s.

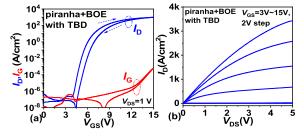

Fig. 3. (a) Transfer and (b) output (DC) characteristics of a vertical MOSFET with TBD process (with additional piranha cleaning).

to 228 mV/dec) and  $V_{\text{th}}$  hysteresis ( $\Delta V_{\text{th}}$ , 1.3 V to 0.8 V) indicate the decreased interface trap states density. The calculated interface trap density ( $N_{\text{it}} = \Delta V_{\text{th}} \times C_{\text{ox}}/q$ ) based on the measured  $\Delta V_{\text{th}}$  with and without piranha cleaning are  $6.2 \times 10^{11}$  cm<sup>-2</sup> and  $1.0 \times 10^{12}$  cm<sup>-2</sup>. In Fig. 2 (b) and (d), the device with additional piranha cleaning shows a reduced DC and gate pulsed *I-V* dispersion, also suggesting a reduced interface trap density. The extracted electron mobility of the inversion channel [4] (considering the drift layer resistance of ~0.33 m $\Omega \cdot \text{cm}^2$  and contact resistance of ~0.15 m $\Omega \cdot \text{cm}^2$ ) is found enhanced from ~30 cm<sup>2</sup>/V-s to ~57 cm<sup>2</sup>/V-s, which can be attributed to the reduced interface (fixed and/or trapped) charges [16], [17]. The ON-state performance of GaN vertical MOSFETs can be effectively improved by reducing interface charges in the gate stack, through the additional piranha cleaning process [18], [19].

The transfer and output characteristics of the device using the same fabrication process with the added TBD are shown in Fig. 3, which exhibits a similar  $I_{ON}/I_{OFF}$  of  $\sim 1 \times 10^9$ , a  $I_G$ of 5.9 × 10<sup>-4</sup> A/cm<sup>2</sup> (at  $V_{GS}$  of 15 V), a  $V_{th}$  of 6.1 V (at  $I_D$ of 1 A/cm<sup>2</sup>), a  $V_{th}$  hysteresis of 0.8 V, a SS of 230 mV/dec, a  $I_{D,max}$  of 3.42 kA/cm<sup>2</sup>, and a  $R_{ON,sp}$  of 0.95 m $\Omega \cdot cm^2$ . It should be noted that although most of the ON-state parameters including the  $I_{ON}/I_{OFF}$ ,  $I_G$  (at  $V_{GS}$  of 15 V),  $V_{th}$ ,  $V_{th}$ hysteresis, and SS are nearly identical in devices with and without TBD, the  $R_{ON,sp}$  in the device with TBD is somewhat ( $\sim 12\%$ ) higher (thereby slightly lower  $I_{D,max}$ ) than the one without TBD, which possibly results from the relatively higher accumulation resistance in the trench region underneath the

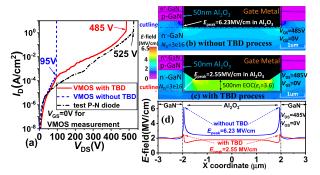

Fig. 4. (a) OFF-state leakage of vertical MOSFETs (with additional piranha cleaning) with & without TBD process and test p-n diode. TCAD simulation results of electric field distribution of VMOSFETs at  $V_{DS}$  = 485 V,  $V_{GS}$  = 0 V (b) without and (c) with a thick bottom dielectric (TBD); (d) electric field distribution along the cutlines at the gate trench bottom.

channel due to a lower carrier concentration in the sidewall and bottom accumulation layer covered by the EOC [22], [23].

Fig. 4(a) compares the OFF-state leakage currents in the vertical MOSFETs (with additional piranha cleaning) with and without the TBD and a p-n<sup>-</sup> diode test structure on the same sample. The device without TBD shows a small  $V_{\rm BR}$ of 95 V due to early dielectric failure at the gate-to-drain MOS junction. The possible reason for the low breakdown voltage could be due to the non-smooth trench bottom surface and damages resulted from the ICP etching for trench formation and/or yet-to-be improved  $Al_2O_3$  quality. In contrast, the  $V_{BR}$ of the device with TBD is greatly enhanced by more than five folds to 485 V, which is close to the  $V_{BR}$  (~525 V) of the p-n diode test structure on the same sample, suggesting an effectively reduced peak electric field in the dielectric. Devices under two cleaning processes (with and without additional piranha cleaning) but without TBD show nearly identical OFFstate performance.

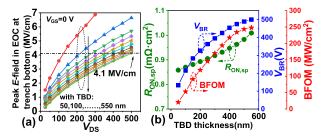

Fig. 4(b), (c) and (d) present the TCAD simulation results of the electric field distribution in gate trench region of vertical MOSFETs without and with the TBD process biased at a  $V_{DS}$ of 485 V and  $V_{GS}$  of 0 V. It is found that the peak electric field  $(E_{\text{peak}})$  in the Al<sub>2</sub>O<sub>3</sub> at the trench bottom corner is suppressed from 6.23 to 2.55 MV/cm using the TBD process, as shown in Fig. 4(d), suggesting the effectiveness of the TBD for electric field management. Fig. 5 (a) shows TCAD simulation results of  $E_{\text{peak}}$  versus  $V_{\text{DS}}$  of devices with varied TBD thickness. Devices with thicker TBD show a reduced  $E_{\text{peak}}$ , resulting in the enhanced  $V_{\text{BR}}$ . Fig. 5(b) illustrates the simulation results of  $R_{ON,sp}$ ,  $V_{BR}$ , and Baliga's figure of merit  $(BFOM = (V_{BR})^2 / R_{ON,sp})$  versus the TBD thickness, showing a trade-off between  $R_{ON,sp}$  and  $V_{BR}$  (thicker TBD results in enhanced  $V_{BR}$  with a cost of higher  $R_{ON,sp}$ ). Introducing thicker TBD can effectively increase the BFOM. However, with the continuous increase of TBD thickness, the enhancement of BFOM tends to saturate.

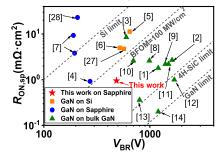

TABLE I summarizes the key device parameters of samples with different fabrication processes. A proper channel cleaning process can effectively improve the ON-state performance and the TBD process can greatly enhance the OFF-state  $V_{BR}$  with minimal sacrifice in  $R_{ON,sp}$  and  $I_{D,max}$ . Fig. 6 benchmarks the  $R_{ON,sp}$  versus  $V_{BR}$  of the quasi-vertical GaN trench MOSFETs under piranha + BOE treatment with TBD in this work with other reported state-of-the-art GaN vertical transistors on bulk GaN substrates and foreign substrates. Our vertical MOSFETs grown on sapphire substrates show a good BFOM

TABLE I SUMMARY OF KEY DEVICE PARAMETERS OF SAMPLES WITH DIFFERENT FABRICATION PROCESSES

| Sample                                        | #1      | #2          | #3          |

|-----------------------------------------------|---------|-------------|-------------|

| channel cleaning                              | BOE     | piranha+BOE | piranha+BOE |

| TBD process                                   | without | without     | with        |

| $V_{\rm th}$ (V) $\hat{@}1$ A/cm <sup>2</sup> | 4.8     | 6.2         | 6.1         |

| $I_{\rm D,max}$ (A/cm <sup>2</sup> )          | 2609    | 3564        | 3421        |

| $R_{\rm ON,sp}({\rm m}\Omega\cdot{\rm cm}^2)$ | 1.03    | 0.85        | 0.95        |

| Peak trans-                                   |         |             |             |

| $conductance(g_m)$                            | 420     | 587         | 538         |

| $(S/cm^2)$ @ $V_{DS}=5V$                      |         |             |             |

| $V_{\rm th}$ hysteresis (V)                   | 1.3     | 0.8         | 0.8         |

| SS (mV/dec)                                   | 281     | 228         | 230         |

| $V_{\rm BR}$ (V)                              | 93      | 95          | 485         |

| BFOM (MW/cm <sup>2</sup> )                    | 8.4     | 10.6        | 248         |

Fig. 5. TCAD simulation results of (a)  $E_{\text{peak}}$  versus  $V_{\text{DS}}$  of devices with varied TBD thickness and (b)  $R_{\text{ON,sp}}$ ,  $V_{\text{BR}}$ , and BFOM versus TBD thickness.  $V_{\text{BR}}$  is defined by the biased  $V_{\text{DS}}$  when the  $E_{\text{peak}}$  in EOC at the trench bottom reaches 4.1 MV/cm (breakdown field of EOC).

Fig. 6. R<sub>ON,sp</sub> versus V<sub>BR</sub> benchmarking of the device with TBD in this work against reported state-of-the-art vertical GaN transistors.

of 248 MW/cm<sup>2</sup>, which is superior to most of the reported vertical transistors on foreign substrates [4]–[7], [27], [28]. The  $V_{\text{BR}}$  of our vertical MOSFETs with TBD can be further improved by (1) optimizing gate trench formation process to achieve a smoother gate trench surface; (2) lowering the Si doping concentration and/or increasing the thickness of the drift layer; (3) introducing proper field plates near the mesa sidewalls [1], [9], [29], [30]. The  $R_{\text{ON,sp}}$  can be further reduced by increasing the doping and thickness of the bottom n<sup>+</sup>-GaN layer [31], [32].

## **IV. CONCLUSION**

In summary, the ON-state performance of GaN vertical trench MOSFETs was effectively improved by reducing interface charges in the gate stack through a proper MOS channel cleaning process (piranha + BOE). In addition, a thick bottom dielectric process has been demonstrated, resulting in a greatly enhanced device OFF-state breakdown voltage with minimal sacrifice in  $R_{ON,sp}$  and  $I_{D,max}$ . Overall highperformance quasi-vertical GaN trench MOSFETs on sapphire are achieved, exhibiting an ultralow  $R_{ON,sp}$  of 0.95 m $\Omega \cdot \text{cm}^2$ , a high  $I_{D,max}$  of 3.4 kA/cm<sup>2</sup>, a large  $V_{th}$  of 6.1 V, and a high  $V_{BR}$  of 485 V.

#### REFERENCES

- [1] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "1.8 mΩ-cm2 vertical GaN-based trench metal–oxide–semiconductor field-effect transistors on a freestanding GaN substrate for 1.2-kV-class operation," *Appl. Phys. Exp.*, vol. 8, no. 5, May 2015, Art. no. 054101, doi: 10.7567/APEX.8.054101.

- [2] T. Oka, T. Ina, Y. Ueno, and J. Nishii, "Over 10 A operation with switching characteristics of 1.2 kV-class vertical GaN trench MOSFETs on a bulk GaN substrate," in *Proc. 28th Int. Symp. Power Semiconductor Devices ICs (ISPSD)*, Prague, Czech Republic, Jun. 2016, pp. 459–462, doi: 10.1109/ISPSD.2016.7520877.

- [3] R. Li, Y. Cao, M. Chen, and R. Chu, "600 V/ 1.7 Ω normally-off GaN vertical trench metal–oxide–semiconductor field-effect transistor," *IEEE Electron Device Lett.*, vol. 37, no. 11, pp. 1466–1469, Nov. 2016, doi: 10.1109/LED.2016.2614515.

- [4] R. Zhu, H. Jiang, C. W. Tang, and K. M. Lau, "Effects of p-GaN body doping concentration on the ON-state performance of vertical GaN trench MOSFETs," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 970–973, Jul. 2021, doi: 10.1109/LED.2021.3080260.

- [5] C. Liu, R. A. Khadar, and E. Matioli, "GaN-on-Si quasi-vertical power MOSFETs," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 71–74, Jan. 2018, doi: 10.1109/LED.2017.2779445.

- [6] R. A. Khadar, C. Liu, R. Soleimanzadeh, and E. Matioli, "Fully vertical GaN-on-Si power MOSFETs," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 443–446, Mar. 2019, doi: 10.1109/LED.2019.2894177.

- [7] C. Gupta, S. H. Chan, Y. Enatsu, A. Agarwal, S. Keller, and U. K. Mishra, "OG-FET: An *in-situ* oxide, GaN interlayer-based vertical trench MOSFET," *IEEE Electron Device Lett.*, vol. 37, no. 12, pp. 1601–1604, Dec. 2016, doi: 10.1109/LED.2016.2616508.

- [8] C. Gupta, C. Lund, S. H. Chan, A. Agarwal, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "*In situ* oxide, GaN interlayer-based vertical trench MOSFET (*OG – FET*) on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 3, pp. 353–355, Mar. 2017, doi: 10.1109/LED.2017.2649599.

- [9] D. Ji, C. Gupta, S. H. Chan, A. Agarwal, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of largearea devices," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, p. 9, doi: 10.1109/IEDM.2017.8268359.

- [10] D. Ji, C. Gupta, A. Agarwal, S. H. Chan, C. Lund, W. Li, S. Keller, U. K. Mishra, and S. Chowdhury, "Large-area *in-situ* oxide, GaN interlayer-based vertical trench MOSFET (OG-FET)," *IEEE Electron Device Lett.*, vol. 39, no. 5, pp. 711–714, May 2018, doi: 10.1109/LED.2018.2813312.

- [11] H. Nie, Q. Diduck, B. Alvarez, A. P. Edwards, B. M. Kayes, M. Zhang, G. Ye, T. Prunty, D. Bour, and I. C. Kizilyalli, "1.5-kV and 2.2-m Ω -cm<sup>2</sup> vertical GaN transistors on bulk-GaN substrates," *IEEE Electron Device Lett.*, vol. 35, no. 9, pp. 939–941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [12] D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, "1.7 kV/1.0 mΩcm<sup>2</sup> normally-off vertical GaN transistor on GaN substrate with regrown p-GaN/AlGaN/GaN semipolar gate structure," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2016, p. 10, doi: 10.1109/IEDM.2016.7838385.

- [13] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-performance GaN vertical fin power transistors on bulk GaN substrates," *IEEE Electron Device Lett.*, vol. 38, no. 4, pp. 509–512, Apr. 2017, doi: 10.1109/LED.2017.2670925.

- [14] Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, p. 9, doi: 10.1109/IEDM.2017.8268357.

- [15] Y. Zhang, M. Sun, J. Perozek, Z. Liu, A. Zubair, D. Piedra, N. Chowdhury, X. Gao, K. Shepard, and T. Palacios, "Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit," *IEEE Electron Device Lett.*, vol. 40, no. 1, pp. 75–78, Jan. 2019, doi: 10.1109/LED.2018.2880306.

- [16] S. K. Powell, N. Goldsman, J. M. McGarrity, and J. Bernstein, "Physics-based numerical modeling and characterization of 6H-siliconcarbide metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 92, pp. 4053–4061, Oct. 2002, doi: 10.1063/1.1499523.

- [17] A. Pérez-Tomás, M. Placidi, X. Perpiñà, A. Constant, P. Godignon, X. Jordà, P. Brosselard, and J. Millán, "GaN metal-oxide-semiconductor field-effect transistor inversion channel mobility modeling," *J. Appl. Phys.*, vol. 105, no. 11, Jun. 2009, Art. no. 114510, doi: 10.1063/1.3140614.

- [18] N. Nepal, N. Y. Garces, D. J. Meyer, J. K. Hite, M. A. Mastro, and C. R. Eddy, "Assessment of GaN surface pretreatment for atomic layer deposited high-K dielectrics," *Appl. Phys. Exp.*, vol. 4, no. 5, May 2011, Art. no. 055802, doi: 10.1143/APEX.4.055802.

- [19] T. Hossain, D. Wei, J. H. Edgar, N. Y. Garces, N. Nepal, J. K. Hite, M. A. Mastro, C. R. Eddy, and H. M. Meyer, "Effect of GaN surface treatment on Al<sub>2</sub>O<sub>3</sub>/n-GaN MOS capacitors," *J. Vac. Sci. Technol. B, Microelectron.*, vol. 33, no. 6, Nov. 2015, Art. no. 061201, doi: 10.1116/1.4931793.

- [20] M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, "GaN-based trench gate metal oxide semiconductor field-effect transistor fabricated with novel wet etching," *Appl. Phys. Exp.*, vol. 1, no. 2, Feb. 2008, Art. no. 021104, doi: 10.1143/APEX.1.021104.

- [21] C. Gupta, D. Ji, S. H. Chan, A. Agarwal, W. Leach, S. Keller, S. Chowdhury, and U. K. Mishra, "Impact of trench dimensions on the device performance of GaN vertical trench MOSFETs," *IEEE Electron Device Lett.*, vol. 38, no. 11, pp. 1559–1562, Nov. 2017, doi: 10.1109/LED.2017.2749540.

- [22] H.-R. Chang, "Trench gate structure with thick bottom oxide," U.S. Patent 4992 390, Feb. 12, 1991.

- [23] J. D. Beasom, "Trench MOS gate device," U.S. Patent 5770878, Jun. 23, 1998.

- [24] A. Agarwal, K. Han, and B. J. Baliga, "Analysis of 1.2 kV 4H-SiC trench-gate MOSFETs with thick trench bottom oxide," in *Proc. IEEE* 6th Workshop Wide Bandgap Power Devices Appl. (WiPDA), Atlanta, GA, USA, Oct. 2018, pp. 125–129, doi: 10.1109/WiPDA.2018.8569070.

- [25] H. Takaya, J. Morimoto, K. Hamada, T. Yamamoto, J. Sakakibara, Y. Watanabe, and N. Soejima, "A 4H-SiC trench MOSFET with thick bottom oxide for improving characteristics," in *Proc. 25th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, Kanazawa, Japan, May 2013, pp. 43–46, doi: 10.1109/ISPSD.2013.6694394.

- [26] C. Gupta, S. H. Chan, C. Lund, A. Agarwal, O. S. Koksaldi, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "Comparing electrical performance of GaN trench-gate MOSFETs with *a*-plane (1120) and *m*-plane (1100) sidewall channels," *Appl. Phys. Exp.*, vol. 9, no. 12, Nov. 2016, Art. no. 121001, doi: 10.7567/APEX.9.121001.

- [27] R. A. Khadar, A. Floriduz, C. Liu, R. Soleimanzadeh, and E. Matioli, "Quasi-vertical GaN-on-Si reverse blocking power MOS-FETs," *Appl. Phys. Exp.*, vol. 14, no. 4, Apr. 2021, Art. no. 046503, doi: 10.35848/1882-0786/abf054.

- [28] Z. Guo, C. Hitchcock, R. F. Karlicek, Jr., G. Piao, Y. Yano, S. Koseki, T. Tabuchi, K. Matsumoto, M. Bulsara, and T. P. Chow, "Integrable quasivertical GaN U-shaped trench-gate metal-oxide-semiconductor fieldeffect transistors for power and optoelectronic integrated circuits," *Phys. Status Solidi (A)*, vol. 217, no. 7, Apr. 2020, Art. no. 1900615, doi: 10.1002/pssa.201900615.

- [29] Y. Zhang, M. Sun, H. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L. Yu, T. Sumitomo, N. A. de Braga, R. V. Mickevicius, and T. Palacios, "Origin and control of OFF-state leakage current in GaNon-Si vertical diodes," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2155–2161, Jul. 2015, doi: 10.1109/TED.2015.2426711.

- [30] K. Nomoto, B. Song, Z. Hu, M. Zhu, M. Qi, N. Kaneda, T. Mishima, T. Nakamura, D. Jena, and H. G. Xing, "1.7-kV and 0.55- mΩ·cm<sup>2</sup> GaN p-n diodes on bulk GaN substrates with avalanche capability," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 161–164, Feb. 2016, doi: 10.1109/LED.2015.2506638.

- [31] Y. Zhang, M. Sun, D. Piedra, J. Hennig, A. Dadgar, and T. Palacios, "Reduction of on-resistance and current crowding in quasi-vertical GaN power diodes," *Appl. Phys. Lett.*, vol. 111, no. 16, Oct. 2017, Art. no. 163506, doi: 10.1063/1.4989599.

- [32] F. Zhou, W. Xu, F. Ren, D. Zhou, D. Chen, R. Zhang, Y. Zheng, T. Zhu, and H. Lu, "High-voltage quasi-vertical GaN junction barrier Schottky diode with fast switching characteristics," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 974–977, Jul. 2021, doi: 10.1109/LED.2021.3078477.