IEEE TRANSACTIONS ON ELECTRON DEVICES

# Tristate Memory Cells Using Double-Peaked Fin-Array III–V Tunnel Diodes Monolithically Grown on (001) Silicon Substrates

Yu Han, Qiang Li, Member, IEEE, and Kei May Lau, Fellow, IEEE

Abstract—We demonstrate functional tristate memory cells using multipeaked GaAs/InGaAs fin-array tunnel diodes grown on exact (001) Si substrates. On-chip connection of single-peaked tunnel diode arrays produces I–V characteristics with multiple negative-differential resistance regions. We designed and fabricated two types of tristate memory cells. In one design, a double-peaked tunnel diode was used as the drive, and a reverse-biased single-peaked tunnel diode was used as the load. In the other design, the tristate memory cell was realized by the series connection of two forward-biased single-peaked tunnel diodes.

*Index Terms*—GaAs fin-array, memory cell, multivalued logic, tunnel diodes.

#### I. INTRODUCTION

S CMOS scaling approaches atomistic and quantum mechanical boundaries, excessive power dissipation and severe RC degradation are becoming more and more pressing issues in present-day binary logic systems [1]. Multivalued logic can potentially overcome these bottlenecks by enhancing signal encoding efficiency and reducing interconnection complexity [2]. Compared with bistable Si MOSFETs, tunnel diodes with negative-differential resistance (NDR) are preferred building blocks for multivalued logic systems [3]–[6]. The picosecond switching characteristics of tunnel diodes (TDs) also favor ultrahigh speed circuit design [7]. Although Si-based resonant interband tunneling diodes and multivalued logic circuitry have been developed [8], III–V-based tunnel diode transistor circuits can potentially deliver superior performance because of the direct bandgap and smaller tunneling mass [9]. Unfortunately, integrating high-performance III-V tunnel diodes onto mainstream (001) Si substrates is challenging due to the large lattice and thermal mismatches. Attempts to grow III-V tunnel diodes on Si usually rely on thick buffer layers to reduce defect density [10]-[14]. Recently, growing III-V nanostructures (including GaAs, InP,

Manuscript received April 19, 2017; revised July 1, 2017 and August 5, 2017; accepted August 9, 2017. This work was supported in part by the Research Grants Council of Hong Kong under Grant 16245216 and in part by Innovation Technology Fund of Hong Kong under Grant ITS/320/14. The review of this paper was arranged by Editor G.-H. Koh. (*Corresponding author: Kei May Lau.*)

The authors are with the Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong (e-mail: yhanaf@connect.ust.hk; eekmlau@ust.hk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2017.2738675

InGaAs, InAs, and GaSb) on Si utilizing the aspect ratio trapping technique in realizing high crystalline quality III-V buffers within a few tens of nanometers has been demonstrated [15]-[22]. Previously, we have reported on the use of III-V FinFET on Si technology to demonstrate GaAs/InGaAs fin-array tunnel diodes and monolithically integrated digital circuits [23]–[25]. Here, we demonstrate the use of the tunnel diode arrays to create tristate memory cells. Multipeaked tunnel diodes were realized via on-chip connection of singlepeaked tunnel diodes electrically isolated by SiO<sub>2</sub> spacers. Combining single-peaked and double-peaked tunnel diodes under forward and reverse biases, we demonstrate functional tristate memory cells on CMOS-compatible on-axis (001) silicon substrates. Compared with traditional CMOS-based binary memories, these tristate memory cells using III-V tunnel diodes could potentially lead to reduced power dissipation, improved operation speed, and high integration density [26]–[30].

#### II. GALLIUM ARSENIDE FIN-ARRAY ON SILICON

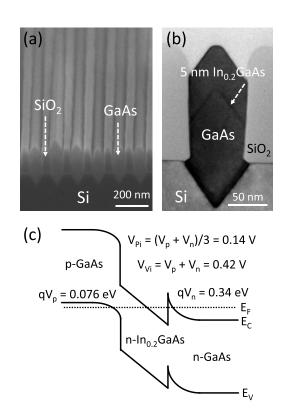

The experiment started with the growth of GaAs fins on patterned (001) Si substrates by metal-organic chemical vapor deposition [23]. V-grooved pockets were formed by anisotropic KOH wet etching. Fig. 1(a), presenting a  $70^{\circ}$ tilted-view scanning electron microscope (SEM) image of the as-grown sample, reveals highly ordered GaAs fin array with two convex (111) facets. Cross-sectional transmission electron microscope (TEM) image of one GaAs fin is displayed in Fig. 1(b). Most of the defects are confined within an ultrathin nucleation layer at the GaAs/Si interface, resulting in good material quality at the junction region. The tunnel junction consists of, from bottom to top, 150-nm-thick carbon-doped p-GaAs  $(3.8 \times 10^{19} \text{ cm}^{-3})$ , 5-nm n-In<sub>0.2</sub>Ga<sub>0.8</sub>As, and 80-nm silicon-doped n-GaAs (>  $1 \times 10^{19}$  cm<sup>-3</sup>). We calibrated the carrier concentration by Hall measurement using thin films on GaAs substrates under the same growth conditions. Fig. 1(c)illustrates the band diagram of the tunnel diode showing the effect of interband tunneling through the thin pseudomorphic InGaAs layer. We calculated the Fermi levels for the highly doped n- and p-GaAs inside the conduction/valance-band using the following equations [31]:

$$qV_n = kT \left\{ \ln \left( \frac{n}{N_C} \right) + 2^{-3/2} \left( \frac{n}{N_C} \right) \right\}$$

(1)

$$qV_p = kT\left\{\ln\left(\frac{p}{N_V}\right) + 2^{-3/2}\left(\frac{p}{N_V}\right)\right\}$$

(2)

Fig. 1. (a)  $70^{\circ}$  tilted-view SEM image of the as-grown highly ordered GaAs fins on Si. (b) Cross-sectional TEM image of the tunnel diode, showing defect confinement inside the V-groove and the 5-nm In<sub>0.2</sub>Ga<sub>0.8</sub>As interlayer. (c) Band diagram of the tunnel junction. Degeneracy of the junction is calculated and labeled.

where  $V_n$  and  $V_p$  are the amount of degeneracy of n-GaAs and p-GaAs, respectively.  $N_C$  and  $N_V$  refer to the effective density of states of the conduction and valance band, while n and p represent the doping levels of the n-GaAs and the p-GaAs regions. At room temperature,  $V_p$  is 0.076 V and  $V_n$  is 0.34 V, based on the calibrated carrier concentrations. The huge difference of  $V_n$  and  $V_p$  mainly stems from the difference of  $N_C$  (4.7 × 10<sup>17</sup> cm<sup>-3</sup>) and  $N_V$  (9 × 10<sup>18</sup> cm<sup>-3</sup>). The intrinsic peak voltage ( $V_{Pi}$ ) refers to the bias necessary to align the maximum electron density to the maximum hole density, while the intrinsic valley voltage ( $V_{Vi}$ ) is the bias to align the conduction band minimum with the valance band maximum. We estimated both  $V_{Pi}$  and  $V_{Vi}$  using (3) and (4) from [32].  $V_{Pi}$  is around 0.14 V and  $V_{Vi}$  is about 0.42 V

$$V_{\rm Pi} = (V_n + V_p)/3$$

(3)

$$V_{\rm Vi} = (V_n + V_p). \tag{4}$$

#### **III.** DEVICE FABRICATION

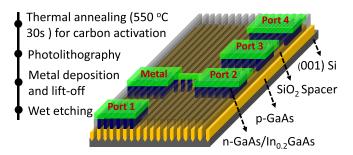

Fig. 2 presents the process flow and schematic of the fabricated double-peaked tunnel diodes and tristate memory cells. Device fabrication started with the activation of hydrogen-passivated carbon in the p-GaAs at 550 °C for 30 s under N<sub>2</sub> ambient. Then, Ni/Ge/Au metal stack was patterned onto the exposed n-GaAs fins. We used wet etching (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 3:1:50) to remove the top n-GaAs/In<sub>0.2</sub>Ga<sub>0.8</sub>As layer and stop at the p-GaAs layer in the unmasked region. Note that tunnel diodes occupying different trenches were electrically isolated by the

Fig. 2. Process flow and schematic of the double-peaked tunnel diode and the tristate memory cells. The size of the electrodes is  $100 \times 100 \ \mu m^2$ .

TABLE I SUMMARY OF THE CIRCUIT FUNCTIONS WHEN PROBING DIFFERENT METAL PADS

| Apply volta | ge Ground | Measured | voltage | Function                |

|-------------|-----------|----------|---------|-------------------------|

| Port 3      | Port 4    | NA       |         | Single peak TD          |

| Port 1      | Port 3    | NA       |         | Double peak TD          |

| Port 1      | Port 4    | Port 3   | Memor   | ry cell (load resistor) |

| Port 4      | Port 1    | Port 2   | М       | emory cell (Load TD)    |

|             |           |          |         |                         |

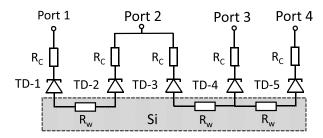

Fig. 3. Equivalent circuit of the fabricated double-peaked tunnel diodes and the tristate memory cells.

SiO<sub>2</sub> spacers. Even though leakage current through the n-Si substrate exists, the amount is negligible compared with the peak current of the tunnel diodes. This feature allows us to achieve on-chip interconnection of individual tunnel diodes in parallel fins. Fig. 3 displays the equivalent circuit of the fabricated devices, with five tunnel diodes connected through four different ports.  $R_C$  corresponds to the contact resistance between the metal stack and the n-GaAs fins, and  $R_W$  refers to the resistance of the partially etched p-GaAs fins. Table I summarizes the circuit functions when probing different metal pads.

## IV. DOUBLE-PEAKED FIN-ARRAY TUNNEL DIODES

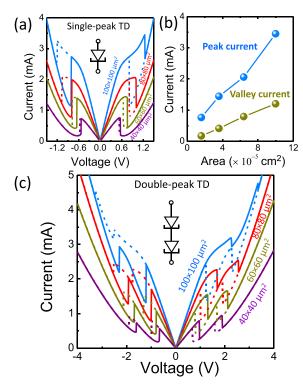

To measure the I-V characteristics of single-peaked tunnel diodes, double sweep from -1.5 to 1.5 V and 1.5 to -1.5 V were applied to Port 3, with Port 4 grounded. With two tunnel junctions connected back to back, at any measurement point, one tunnel diode was forward biased and the other was reverse biased (behaving like a resistor). As a result, we observed symmetric NDR regions, as shown in Fig. 4(a). Due to the parasitic resistance, both peak and valley voltages are larger than the intrinsic values. Besides, since the value

Fig. 4. (a) *HV* characteristic of single-peaked tunnel diodes with different sizes. Solid curves refer to sweeping forward and dotted curve sweeping backward. (b) Linear scaling of peak current and valley current with device sizes. (c) *HV* characteristic of double-peaked tunnel diodes with different sizes. Solid curves refer to sweeping forward and dotted curves sweeping backward.

of parasitic resistance is larger than that of NDR, hysteresis is observed under the double-sweep condition and aggravates as device size increases due to unmatched scaling of NDR and the contact resistance. Fig. 4(b) indicates the linear scaling of peak current and valley current with device size. When measuring the I-V characteristic at Port 3 with Port 1 grounded, a double-peaked tunnel diode was formed by the series connection of two single-peaked tunnel diodes. At either forward or reverse bias, two tunnel diodes were forward biased and the other two reverse biased. The measured curves are shown in Fig. 4(c). We observed double-peaked characteristic and hysteresis in all the measured devices.

# V. DOUBLE-STATE MEMORY CELLS

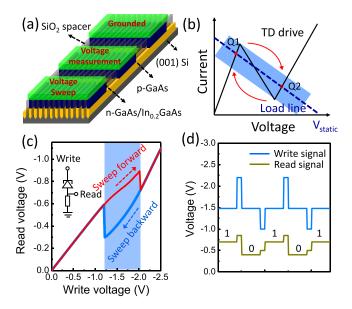

We first fabricated a two-state memory cell to illustrate the working principle of tunnel diode-based memory circuits. Fig. 5(a) shows the schematic of a two-state memory cell using one forward-biased single-peaked tunnel diode as drive and another reverse-biased counterpart (serving as a resistor) as load. Detailed electrical analysis of this structure can be found in [24] and [25]. Fig. 5(b) presents the load line analysis. With a properly selected static input voltage  $V_{\text{static}}$ , two stable working points (Q1 and Q2) can be realized. This bistable condition can only be obtained when the value of load resistance exceeds that of the NDR. These working states (Q1 and Q2) could be regarded as stored digital values inside a memory cell. Changing the working points requires a writing pulse at the input end. A sudden increase of the write voltage would move the load line to pass through the peak

Fig. 5. (a) Schematic of the double-state memory cell. (b) Load line analysis showing the basic principle of a two-state memory cell composed of a single-peak tunnel diode connected with a resistor. Shaded area indicates double states. (c) Measured output (read) voltage of the load resistor when sweeping the write voltage forward and backward. Shaded area indicates double states. (d) Waveforms showing the function of the two-state memory cell at static write voltage of -1.48 V. Writing pulses change the stored value.

of the tunnel diode and the subsequent return to the  $V_{\text{static}}$ would shift the working point to Q2. The switching of the working points could be illustrated more clearly in Fig. 5(c), plotting the measured output (read) voltage across the load resistor when sweeping the input (write) voltage forward and backward. When sweeping forward, the read voltage increased linearly with the write voltage, and then underwent a sudden slump when the write voltage approached -2.02 V. This reveals the transition from the bistable condition to the monostable condition as indicated by the upper red arrow in Fig. 5(b). Similarly, when sweeping backward, an abrupt jump of read voltage occurred as the write voltage approached -1.22 V [corresponding to the lower red arrow in Fig. 5(b)]. For any write voltage falling between -1.22 and -2.02 V, there are two possible read voltages as indicated by the blueshaded regions. The two stable read voltages corresponds to the working points (Q1 and Q2) shown in Fig. 5(b). For an initial state Q1, a write pulse smaller than -2.02 V would shift the circuit from bistable to monostable condition, and then to state Q2. Analogously, for an initial state Q2, a write pulse larger than -1.22 V would shift the working point to Q1. For example, with an initial stored voltage of -0.7 V, a writing pulse of -2.2 V would change the stored value to -0.4 V while a -1 V pulse moves the state back to -0.7 V. The corresponding waveforms illustrating the state-changing function is presented in Fig. 5(d). The ranges of the voltage for the stored digital values ("0" and "1") are: -0.30 to -0.72 V and -0.59 to -0.89 V, respectively. The noise margin of each state could be defined as the minimum value of the voltage difference between the operating point and the minimum of the read voltage, and the voltage difference between operating point and the maximum of the read voltage [33]. Thus, at a

Fig. 6. (a) Measured output (read) voltage of the load resistor when sweeping the write-voltage forward and backward. Shaded area indicates tristates. (b) Load-line analysis showing the basic principle of tristate memory cells based on double-peaked tunnel diodes. Shaded area indicates tristates. (c) Waveforms showing the function of the tristate memory cell at -2.65 V static write voltage. -0.82, -0.68, and -0.43 V refers to logic states "2," "1," and "0," respectively.

static write voltage of -1.48 V, a noise margin of 0.1 and 0.11 V is extracted for states "0" and "1," respectively.

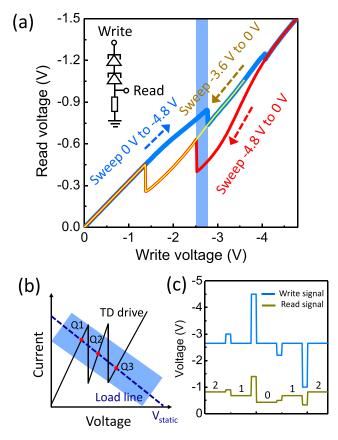

# VI. TRISTATE MEMORY CELLS

A tristate memory cell was then built by applying the write voltage at Port 1 and extracting the read voltage from Port 3 in Figs. 2 and 3. Voltage sweep from 0 to -4.8 V, -4.8 to 0 V, and -3.6 to 0 V was applied to Port 1, with Port 4 grounded. Fig. 6(a) presents the relationship of the read voltage and the write voltage under different sweeping conditions. Singlevalued read voltage is observed when the write voltage is larger than -1 V or smaller than -4 V. Two possible read voltages are obtained when the write voltage falls between -1.38 and -2.53 V or -2.76 and -4.06 V. For write voltage ranging from -2.53 to -2.76 V, we observed a tristate output region with one write voltage corresponding to three possible read voltages as highlighted by the blue shade. The mechanism of this multivalued output is explained as follows. A tristate memory cell can be built by connecting a double-peaked tunnel diode with a load resistor. When applying a negative voltage at Port 1 with Port 4 grounded, both TD-1 and TD-3 were forward biased (serving as single-peak tunnel diode), and TD-2 and TD-5 were reversed biased (serving as resistor). The series connection of TD-1 and TD-3 formed a double-peaked tunnel diode and the reversed biased TD-5 served as the

TABLE II VALUE OF WRITING PULSE REQUIRED FOR CHANGING THE STORED LOGIC STATES

| Value change          | Writing pulse (V) |

|-----------------------|-------------------|

| $0 \longrightarrow 1$ | -2.53 < V < -1.38 |

| $0 \longrightarrow 2$ | V > -1.38         |

| $1 \longrightarrow 0$ | V < -4.06         |

| $1 \longrightarrow 2$ | V > -1.38         |

| $2 \longrightarrow 0$ | V < -4.06         |

| $2 \longrightarrow 1$ | -4.06 < V < -2.76 |

load resistor. The load-line analysis in Fig. 6(b) indicates the basic working principle of this tunnel diode-based tristate memory cell. Three stable working points (Q1, Q2, and Q3) can be clearly detected when selecting a proper load resistance and a static write voltage. Each working point can be regarded as a stored digital value and the stored value can be altered by a writing pulse at the input end. Given an initial working point of Q1, a small writing pulse would move the load line to pass through the first peak of the double-peaked tunnel diode, and then return to the working point of Q2. Similarly, a large writing-pulse would move the load line to pass through the second peak, and then return to the working point of Q3. For example, given a write voltage of -2.65 V and an initial stored voltage of -0.82 V (regarded as digit "2"), applying a pulse between -2.76 and -4.06 V would change the stored value to -0.68 V (regarded as digit "1"). Similarly, another pulse smaller than -4.06 V would change the stored value further to -0.43 V (regarded as digit "0"). The ranges of voltage for different states "0," "1," and "2" extracted from Fig. 6(a) are: -0.49 to -0.40 V, -0.74 to -0.63 V, and -0.84 to -0.78 V, respectively. At a static write voltage of -2.65 V, a noise margin of 30, 50, and 20 mV could be extracted for states "0," "1," and "2." The noise margin of this tristate memory cell is determined by the first peak and second valley of the double-peaked tunnel diode, as bounded by the edges of the blue shade in Fig. 6(b). Larger noise margin could be obtained by improving the peak current density and the peak to valley current ratio of the double-peaked tunnel diode. Fig. 6(c) presents the waveforms of the writing and the reading functions, and Table II summarizes the write pulses necessary to alter the stored values.

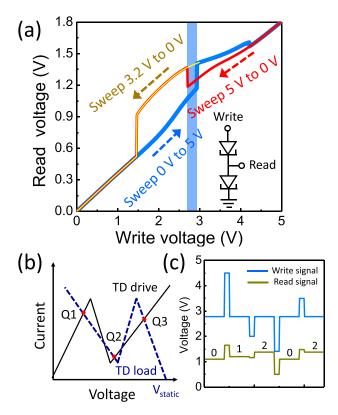

Another type of tristate memory cell was realized using a different connection method. Shown in Fig. 7(a) are voltage sweeps from 0 to 5 V, 5 to 0 V and 3 to 0 V applied at Port 4 with Port 1 grounded and the read voltage was measured at Port 2 (as shown in Figs. 2 and 3). For the write voltage falling between 2.71 and 2.93 V, we detected three possible read voltages within the shaded region. During the measurement, TD-1 and TD-3 were forward biased and TD-2 and TD-5 were reversed biased. This configuration can be simplified as two tandem single-peaked tunnel diodes. The measured read voltage was, thus, the voltage drop at one forward-biased single-peaked tunnel diode. As indicated by

Fig. 7. (a) Measured output (read) voltage of the load tunnel diode when sweeping the write voltage forward and backward. Shaded area indicates tristates region. (b) Load line analysis showing the basic principle of the tristate memory cell based on tandem single-peaked tunnel diodes. (c) Waveforms showing the functions of the tristate memory cell at 2.78 V static write voltage. 1.38, 1.2, and 1.10 V refer to logic states "2," "1," and "0," respectively.

the load-line analysis in Fig. 7(b), three stable working points (Q1, Q2, and Q3) could be realized at the intersection of the positive differential resistance regions of the two single-peaked tunnel diodes. These three different working points can be seen as stored digital values of the memory cell. Changing the stored values requires a writing pulse. Note that the switching sequence of the working points in the load line analysis depends on the peak current difference of the drive and load tunnel diodes, which may result from process nonuniformity. The most efficient and clear method to determine the switching sequence is through the measurement presented in Fig. 7(a). Details of the three working points and writing pulses can be precisely extracted. For example, as shown in Fig. 7(c), the stored value changes from "0" to "1", and then to "2," when a 4.5 V pulse and a subsequent 2 V pulse are applied. The voltage ranges for different states "0," "1," and "2" are: 1.07 to 1.17 V, 1.18 to 1.26 V, and 1.37 to 1.41 V, respectively. Given a static write voltage of 2.78 V, we can determine the noise margin of states "0," "1," and "2" as 30, 20, and 10 mV. As shown in Fig. 7(b), the noise margin of this tristate memory cell is closely associated with the peak voltage, valley voltage, and projected peak voltage (has same current value with the peak voltage in the I-V curve) of the load/drive tunnel diodes. Expansion of the tristate region is possible through increasing the voltage swing (voltage difference between the peak voltage and projected peak voltage) of the tunnel diodes.

TABLE III VALUE OF WRITING PULSE REQUIRED FOR CHANGING THE STORED LOGIC STATES

| Value change          | Writing pulse (V) |  |

|-----------------------|-------------------|--|

| $0 \longrightarrow 1$ | V > 4.21          |  |

| $0 \longrightarrow 2$ | 2.93 < V < 4.21   |  |

| $1 \longrightarrow 0$ | V < 1.47          |  |

| $1 \longrightarrow 2$ | 1.47 < V < 2.71   |  |

| $2 \longrightarrow 0$ | V < 1.47          |  |

| $2 \longrightarrow 1$ | V > 4.21          |  |

We summarize the values of the writing pulses necessary to alter the stored digits in Table III.

## VII. CONCLUSION

In conclusion, we have demonstrated two types of tristate memory cells using double-peaked GaAs/InGaAs fin-array tunnel diodes grown on exact (001) Si substrates by selective epitaxy. The stored digital states of the memory cells can be controlled by the writing pulses, and the pulse value determines the next transition state. These results show promises for realizing III–V tunnel diode-based multivalued logic systems on Si substrates.

#### ACKNOWLEDGMENT

The authors would like to thank SEMATECH, Austin, TX, USA, for providing the initial patterned Si substrates and the NFF and MCPF of HKUST, Hong Kong, for technical support.

## REFERENCES

- A. Allan, D. Edenfeld, W. H. Joyner, A. B. Kahng, M. Rodgers, and Y. Zorian, "2001 technology roadmap for semiconductors," *Computer*, vol. 35, no. 1, pp. 42–53, Jan. 2002, doi: 10.1109/2.976918.

- [2] P. Mazumder, S. Kulkarni, M. Bhattacharya, J. P. Sun, and G. I. Haddad, "Digital circuit applications of resonant tunneling devices," *Proc. IEEE*, vol. 86, no. 4, pp. 664–686, Apr. 1998, doi: 10.1109/5.663544.

- [3] H. C. Lin, "Resonant tunneling diodes for multivalued digital applications," in *Proc. Int. Symp. Multiple-Valued Logic*, 1994, pp. 188–195, doi: 10.1109/ISMVL.1994.302201.

- [4] L. Worschech *et al.*, "Universal and reconfigurable logic gates in a compact three-terminal resonant tunneling diode," *Appl. Phys. Lett.*, vol. 96, no. 4, p. 042112, Jan. 2010, doi: 10.1063/1.3302457.

- [5] F. Capasso *et al.*, "Quantum functional devices: Resonant-tunneling transistors, circuits with reduced complexity and multiple-valued logic," *IEEE Trans. Electron Devices*, vol. 36, no. 10, pp. 2065–2082, Oct. 1989, doi: 10.1109/16.40888.

- [6] M.-H. Shieh and H. C. Lin, "Modeling hysteretic current-voltage characteristics for resonant tunneling diodes," *IEEE Trans. Comput. Aided Design Integr.*, vol. 14, no. 9, pp. 1098–1103, Sep. 1995, doi: 10.1109/16.40888.

- [7] C. T. Van Degrift, "Tunnel diode oscillator for 0.001 PPM measurements at low temperatures," *Rev. Sci. Instrum.*, vol. 46, no. 5, pp. 599–607, May 1975. DOI: 10.1063/1.1134272

- [8] N. Jin *et al.*, "Tri-state logic using vertically integrated Si-SiGe resonant interband tunneling diodes with double NDR," *IEEE Electron Device Lett.*, vol. 25, no. 9, pp. 646–648, Sep. 2004, doi: 10.1109/LED.2004.833845.

- [9] D. Pawlik *et al.*, "Benchmarking and improving III-V Esaki diode performance with a record 2.2 MA/cm2 peak current density to enhance TFET drive current," in *IEDM Tech. Dig.*, Dec. 2012, pp. 27.1.1–27.1.3, doi: 10.1109/IEDM.2012.6479118.

- [10] S. L. Rommel *et al.*, "Record PVCR GaAs-based tunnel diodes fabricated on Si substrates using aspect ratio trapping," in *IEDM Tech. Dig.*, Dec. 2008, pp. 30.6.1–30.6.4, doi: 10.1109/IEDM.2008.4796801.

- [11] W. Prost *et al.*, "High performance III/V RTD and PIN diode on a silicon (001) substrate," *Appl. Phys. A*, vol. 87, no. 3, pp. 539–544, Jun. 2007, doi: 10.1007/s00339-007-3920-1

- [12] C. D. Bessire, M. T. Björk, H. Schmid, A. Schenk, K. B. Reuter, and H. Riel, "Trap-assisted tunneling in Si-InAs NW heterojunction tunnel diodes," *NanoLetters*, vol. 11, no. 10, pp. 4195–4199, Oct. 2011, doi: 10.1021/nl202103a.

- [13] T. Yang, S. Hertenberger, S. Morkötter, G. Abstreiter, and G. Koblmüller, "Size, composition, and doping effects on In (Ga) As nanowire/Si tunnel diodes probed by conductive atomic force microscopy," *Appl. Phys. Lett.*, vol. 101, no. 23, pp. 233102-1–233102-5, Dec. 2012, doi: 10.1063/1.4768001.

- [14] P. Thomas *et al.*, "Performance Evaluation of In<sub>0.53</sub>Ga<sub>0.47</sub>As Esaki tunnel diodes on silicon and InP substrates," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2450–2456, Aug. 2015, doi: 10.1109/TED.2015.2445731.

- [15] J. Z. Li *et al.*, "Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping," *Appl. Phys. Lett.*, vol. 91, no. 2, pp. 021114-1–021114-3, Jul. 2007, doi: 10.1063/1.2756165

- [16] W. Guo *et al.*, "Selective metal-organic chemical vapor deposition growth of high quality GaAs on Si (001)," *Appl. Phys. Lett.*, vol. 105, no. 6, pp. 062101-1–062101-3, Aug. 2014, doi: 10.1063/1.4892468.

- [17] R. Cipro *et al.*, "Low defect InGaAs quantum well selectively grown by metal organic chemical vapor deposition on Si (100) 300 mm wafers for next generation non planar devices," *Appl. Phys. Lett.*, vol. 104, no. 26, p. 262103, Jul. 2014, doi: 10.1063/1.4886404.

- [18] N. Waldron *et al.*, "InGaAs gate-all-around nanowire devices on 300 mm Si substrates," *IEEE Electron Device Lett.*, vol. 35, no. 11, pp. 1097–1099, Nov. 2014, doi: 10.1109/LED.2014.2359579

- [19] Q. Li, K. W. Ng, and K. M. Lau, "Growing antiphase-domain-free GaAs thin films out of highly ordered planar nanowire arrays on exact (001) silicon," *Appl. Phys. Lett.*, vol. 106, no. 7, pp. 072105-1–072105-4, Feb. 2015, doi: 10.1063/1.4913432

- [20] C. Merckling *et al.*, "Heteroepitaxy of InP on Si(001) by selective-area metal organic vapor-phase epitaxy in sub-50 nm width trenches: The role of the nucleation layer and the recess engineering," *J. Appl. Phys.*, vol. 115, no. 2, p. 023710, 2014, doi: 10.1063/1.4862044.

- [21] Y. Han, Q. Li, S. P. Chang, W. D. Hsu, and K. M. Lau, "Growing InGaAs quasi-quantum wires inside semi-rhombic shaped planar InP nanowires on exact (001) silicon," *Appl. Phys. Lett.*, vol. 108, no. 24, p. 242105, Jun. 2016, doi: 10.1063/1.4953839.

- [22] T. Orzali *et al*, "Epitaxial growth of GaSb and InAs fins on 300 mm Si (001) by aspect ratio trapping," *J. Appl. Phys.*, vol. 120, no. 8, p. 085308, 2016, doi: 10.1063/1.4961522.

- [23] Q. Li, Y. Han, X. Lu, and K. M. Lau, "GaAs-InGaAs-GaAs fin-array tunnel diodes on (001) Si substrates with room-temperature peak-tovalley current ratio of 5.4," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 24–27, Jan. 2016, doi: 10.1109/LED.2015.2499603.

- [24] Y. Han, Q. Li, and K. M. Lau, "Monolithic integration of tunnel diodebased inverters on exact (001) Si substrates," *IEEE Electron Device Lett.*, vol. 37, no. 6, pp. 717–720, Jun. 2016, doi: 10.1109/LED.2016.2552219.

- [25] Y. Han, Q. Li, and K. M. Lau, "Fin-array tunneling trigger with tunable hysteresis on (001) silicon substrate," *IEEE Electron Device Lett.*, vol. 38, no. 5, pp. 556–559, May 2017, doi: 10.1109/LED.2017.2689027.

- [26] K. Karda, S. Sutar, J. Brockman, J. Nahas, and A. Seabaugh, "Bistablebody tunnel SRAM," *IEEE Trans. Nanotechnol.*, vol. 11, no. 6, pp. 1067–1072, Jun. 2010, doi: 10.1109/TNANO.2010.2053555.

- [27] P. Berger, "Compact memory structure including tunneling diode," U.S. Patent 15 255 788, Sep. 2, 2016.

- [28] V. Mikhelashvili *et al.*, "Non-volatile memory transistor based on Pt nanocrystals with negative differencial resistance," *J. Appl. Phys.*, vol. 112, no. 2, p. 024319, Jul. 2012, doi: 10.1063/1.4739714.

- [29] A. Seabaugh et al., "Transistors and tunnel diodes for analog/mixedsignal circuits and embedded memory," in Int. Elect. Dev. Meeting Tech. Dig., Dec. 1998, pp. 429–432, doi: 10.1109/IEDM.1998.746390.

- [30] J. P. A. van der Wagt, "Tunneling based SRAM," Proc. IEEE, vol. 87, no. 4, pp. 571–595, Apr. 1999, doi: 10.1109/5.752516.

- [31] W. B. Joyce and R. W. Dixon, "Analytic approximations for the Fermi energy of an ideal Fermi gas," *Appl. Phys. Lett.*, vol. 31, pp. 354–356, Jun. 1977, doi: 10.1063/1.89697.

- [32] T. A. Demassa and P. K. David, "The prediction of tunnel diode voltage-current characteristics," *Solid-State Electron.*, vol. 13, no. 2, pp. 131–138, 1970, doi: 10.1016/0038-1101(70)90043-2.

- [33] S.-J. Wei and H. C. Lin, "Multivalued SRAM cell using resonant tunneling diodes," *IEEE J. Solid-State Circuits*, vol. 27, no. 2, pp. 212–216, Feb. 1992, doi: 10.1109/4.127345.

Yu Han received the B.S. degree in optical information from the Huazhong University of Science and Technology, Wuhan, China, in 2014. He is currently pursuing the Ph.D. degree with the Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong.

His current research focuses on growing III–V nanostructures on (001) Si for optoelectronic applications.

Qiang Li (S'12–M'15) received the B.S. degree from Peking University, Beijing, China, in 2009, and the Ph.D. from The Hong Kong University of Science and Technology, Hong Kong, in 2014.

He is currently a Research Assistant Professor with the Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology.

Kei May Lau (S'78–M'80–SM'92–F'01) received the B.S. and M.S. degrees in physics from the University of Minnesota, Minneapolis, MN, USA, and the Ph.D. degree in electrical engineering from Rice University, Houston, TX, USA.

She is currently a Fang Professor of engineering with The Hong Kong University of Science and Technology, Hong Kong. She is an Editor of *EDL* and an Associate Editor of *Applied Physics Letters*.