Phys. Status Solidi A, 1-4 (2014) / DOI 10.1002/pssa.201300495

## *In situ* SiN<sub>x</sub> gate dielectric by MOCVD for low-leakage-current ultra-thin-barrier AIN/GaN MISHEMTs on Si

## Xing Lu, Jun Ma, Zhaojun Liu, Huaxing Jiang, Tongde Huang, and Kei May Lau\*

Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Clear Water Bay, Hong Kong

Received 24 August 2013, revised 28 January 2014, accepted 24 February 2014 Published online 26 March 2014

Keywords AlN/GaN, in situ SiN<sub>x</sub>, low leakage current, MISHEMTs

\* Corresponding author: e-mail eekmlau@ust.hk, Phone: +852 2358 7049, Fax: +852 2358 1485

In situ SiN<sub>x</sub> grown by metal-organic chemical vapor deposition (MOCVD) was employed as the gate dielectric for ultra-thinbarrier AlN/GaN metal-insulator-semiconductor high electron mobility transistors (MISHEMTs) on Si substrates. Despite the ultra-thin barrier of 1.5 nm, low reverse leakage current of below  $10^{-7}$  A cm<sup>-2</sup> was obtained with a 7 nm *in situ* SiN<sub>x</sub> gate dielectric. The good surface passivation effects of *in situ* SiN<sub>x</sub> were also

1 Introduction GaN-based HEMTs have been established as excellent candidates for microwave power applications, due to their capability of higher power densities at higher frequencies as compared to Si and GaAs-based devices. The ever-increasing demand for high-speed highpower devices has prompted much research recently in optimizing the barrier design of GaN-based HEMTs, including AlGaN, AlN, lattice matched InAlN, and quaternary InAlGaN [1]. Among these III-Nitride heterostructures, AlN/GaN offers the highest theoretical 2DEG sheet charge density from a combination of maximum spontaneous and piezoelectric polarizations. In addition, the AlN barrier, with its high dielectric constant (8.5) and wide band gap (6.2 eV), provides better carrier confinement and a larger breakdown field. The use of an ultra-thin AlN barrier laver also increases the intrinsic transconductance and decreases the short channel effects by placing the gate much closer to the 2DEG channel. Recently, high-quality AlN/ GaN epitaxial growth has been reported with large 2DEG concentration  $(>2 \times 10^{13} \text{ cm}^{-2})$  and high mobility (>1200 $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ) for extremely thin AlN barriers (<6 nm) [2–4].

Despite the excellent progress of AlN/GaN devices to date, there are still significant challenges to be overcome before they can be fully commercialized. Having a very thin AlN barrier layer, of only a few nm, the devices suffer from demonstrated by the enhanced source/drain (S/D) current density and the reduced drain current degradation. Furthermore, interface trapping effects in the *in situ* SiN<sub>x</sub>/AIN/GaN heterostructures were investigated by double-mode capacitance–voltage (*C*–*V*) measurements and frequency dependent conductance analysis. A trap states density of  $1.9-3.4 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> with a time constant of 0.8–17 µs were deduced.

© 2014 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim

surface sensitivity and large gate leakage currents unless the epilayers are well protected [5]. Previously, several dielectrics such as Al<sub>2</sub>O<sub>3</sub> [1, 2, 5, 6], SiN<sub>x</sub> [7], HfO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub> [8, 9] have been explored as gate insulators. However, these insulators are deposited *ex situ*, which can introduce additional growth- and process-related defects on the devices. Limited work has been reported using *in situ* SiN<sub>x</sub> on an AlN/GaN structure with successful suppression of gate leakage current [10]. It was even found that the *in situ* SiN<sub>x</sub> gate dielectrics can lead to larger gate leakage when compared with the *ex situ* deposited ones [11]. On the other hand, *in situ* SiN<sub>x</sub> cap layer grown on AlN/GaN HEMTs has been reported previously for surface passivation rather than gate dielectric [4]. The SiN<sub>x</sub> in the gate region was selectively removed during the device fabrication.

In this study, *in situ*  $SiN_x$  by metal-organic chemical vapor deposition (MOCVD) was employed as the gate dielectric for ultra-thin-barrier AlN/GaN metal-insulator-semiconductor high electron mobility transistors (MIS-HEMTs) on Si substrates. Both material and electrical characterizations were performed to quantify the performance of the *in situ*  $SiN_x$  film.

**2 Experiments** The *in situ*  $SiN_x/AIN/GaN$  MIS-HEMT structures were grown by MOCVD on 2-inch Si

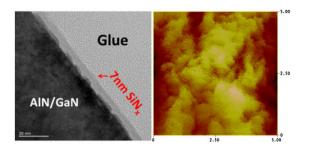

**Figure 1** TEM (left) and AFM (right) images of the 7 nm *in situ*  $SiN_x$  layer deposited by MOCVD.

(111) substrates. The epilayers consist of, from bottom to top, a 45 nm AlN nucleation layer, 1.3 µm strain/resistivityengineering buffer layers, a 1 µm GaN layer, followed by a 1.5 nm AlN barrier layer and a 3 or 7 nm in situ  $SiN_x$  cap layer. The in situ SiN<sub>x</sub> was deposited using silane and ammonia immediately after the AlN/GaN heterostructure growth in the MOCVD chamber at 1145 °C. Atomic force microscopy (AFM) and transmission electron microscopy (TEM) observations of the sample with 7 nm in situ SiN<sub>x</sub> showed a smooth surface morphology and uniform coverage, as shown in Fig. 1. The root mean square (RMS) roughness across a  $5 \,\mu\text{m} \times 5 \,\mu\text{m}$  scanned area is 2.36 nm. Fabrication of MISHEMTs began with mesa etching for device isolation using a CF<sub>4</sub>/O<sub>2</sub>-based reactive ion etching (RIE) followed by a Cl<sub>2</sub>-based inductively coupled plasma (ICP) etching. The mesa depth was around 120 nm. After removing the  $SiN_x$  cap layer in the S/D region by RIE, Ti/Al/Ni/Au (20/150/50/80 nm) was deposited by e-beam evaporation and annealed at 850 °C in N<sub>2</sub> ambient to form S/D ohmic contacts. Finally, the gate metal was formed by e-beam evaporation of Ni/Au and a lift-off process.

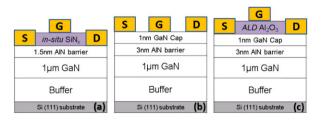

In this study, MISHEMTs with 1  $\mu$ m gate length ( $L_{\rm G}$ ) and 1  $\mu$ m gate-to-source/gate-to-drain distance ( $L_{\rm GS}/L_{\rm GD}$ ), circular-shaped MIS diodes of 200  $\mu$ m in diameter and transmission-line matrix (TLM) structures were fabricated on the samples with different SiN<sub>x</sub> thicknesses and characterized. Moreover, identical GaN (1 nm)/AlN (3 nm)/GaN HEMTs and Al<sub>2</sub>O<sub>3</sub> (7 nm)/GaN (1 nm)AlN (3 nm)/GaN MOSHEMTs in our previous work [6] were used as reference. The cross-sectional schematics of the three device structures are illustrated in Fig. 2. In this work,

**Figure 2** Cross-section of the *in situ*  $SiN_x/AlN/GaN$  MISHEMT (a), the GaN/AlN/GaN HEMT (b), and the Al<sub>2</sub>O<sub>3</sub>/GaN/AlN/GaN MOSHEMT (c). (Note that the figure is not drawn to scale.)

the *in situ*  $SiN_x$  cap layer effectively prevented relaxation of the AlN barrier during the post-growth cooling process, as confirmed by the AFM image in Fig. 1. Thus, the previously used 1 nm GaN surface protection layer was omitted.

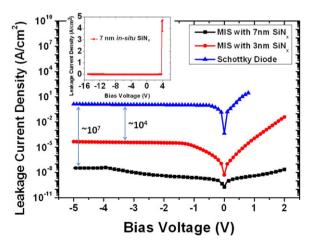

**3** Results and discussion The current–voltage (*I–V*) characteristics of the circular MIS diodes and the reference Schottky diode are plotted in Fig. 3. At a negative bias of -5 V, the reverse leakage current of the MIS diodes with 7 and 3 nm *in situ* SiN<sub>x</sub> were about 7 and 4 orders of magnitude lower than that of the reference GaN/AlN/GaN Schottky diode, respectively. The leakage current density of the MIS diode with 7 nm *in situ* SiN<sub>x</sub> was on the order of  $10^{-7}$  A cm<sup>-2</sup>, remarkably lower than that of similar structures using other dielectrics [5–9]. The breakdown voltage of the 7 nm *in situ* SiN<sub>x</sub> was 4 V, as shown in the inset of Fig. 3.

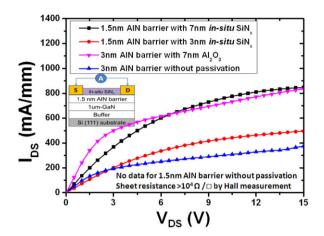

According to TLM measurements, the sheet resistances of the two MISHEMT samples were around  $1300 \,\Omega/\Box$ (with 7 nm *in situ* SiN<sub>x</sub>) and  $4200 \Omega/\Box$  (with 3 nm *in situ*  $SiN_r$ ), respectively, which were about one order lower than that of the 1.5-nm-barrier GaN/AlN/GaN HEMT sample without surface passivation [1]. To further evaluate the effectiveness of the *in situ*  $SiN_r$  thin film as a passivation layer, the I-V characteristics between the source and drain terminals for all four samples were performed, as shown in Fig. 4. The current density has been largely enhanced by both the *in situ* SiN<sub>x</sub> and Al<sub>2</sub>O<sub>3</sub> passivation. The improvement is due to reduced AlN relaxation, increased carrier concentration and surface protection effects [6]. The different slopes of the saturated current in the cases of the *in situ*  $SiN_x$  and  $Al_2O_3$  passivation can be explained by the different AlN barrier thicknesses, different surface scattering effects, as well as the different surface potential induced by the GaN surface protection layer in the Al<sub>2</sub>O<sub>3</sub> MOSHEMT sample, because the current is a strong function

**Figure 3** Leakage current of a GaN/AlN/GaN Schottky diode with 3 nm AlN barrier and two 1.5-nm-barrier MIS diodes with 3 and 7 nm *in situ* SiN<sub>x</sub>. The inset shows the breakdown voltage of the 7 nm *in situ* SiN<sub>x</sub>.

3

**Figure 4** I-V characteristics between the source and drain terminals for all four samples. The inset shows the measured schematic with 3  $\mu$ m source–drain spacing.

of 2DEG density and electron mobility. When comparing the two MISHEMT samples, thicker *in situ*  $SiN_x$  layer led to a higher current density, suggesting better surface passivation effects. Similar phenomenon has also been observed with other dielectrics [6, 12].

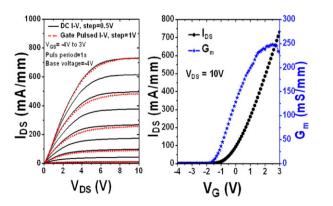

A fabricated MISHEMT with 7 nm *in situ* SiN<sub>x</sub> exhibited a peak transconductance of 248 mS mm<sup>-1</sup> and a maximum drain current density of 730 mA mm<sup>-1</sup>, as shown in Fig. 5. DC-RF dispersion of this MISHEMT was also characterized to verify the effectiveness of the *in situ* SiN<sub>x</sub> passivation [6]. A 500  $\mu$ s pulsed voltage was applied to the gate with the base voltage at -4V (quiescent bias at pinch-off condition). Negligible current degradation as shown in Fig. 5 (left) confirms the good surface passivation effect of the *in situ* SiN<sub>x</sub> layer.

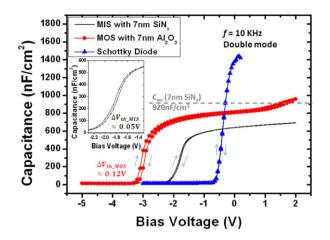

To characterize interfacial traps, double-mode C-V measurements of a MIS diode with 7 nm *in situ* SiN<sub>x</sub>, a MOS diode with 7 nm Al<sub>2</sub>O<sub>3</sub> and a Schottky diode were made and are illustrated in Fig. 6. The measurements were set up with an up-and-down sweep rate of 0.05 V s<sup>-1</sup> and a voltage

**Figure 6** 10 kHz double-mode C-V characteristics of a MIS diode with 7 nm *in situ* SiN<sub>x</sub>, a MOS diode with 7 nm Al<sub>2</sub>O<sub>3</sub> and a Schottky diode. The inset shows the enlargement of the hysteresis for the MIS diode.

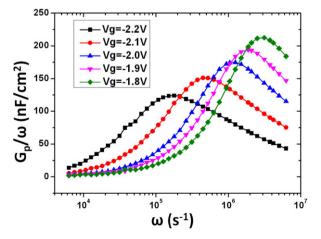

variation of 50 mV at 10 kHz. No measurable hysteresis was observed for the Schottky diode, while a 0.05 and a 0.12 V clockwise hysteresis ( $\Delta V_{\text{th}}$ ) appeared for the MIS and MOS diodes, respectively. Such hysteresis is believed to be resulted from acceptor-like states in the dielectrics or at the dielectric/barrier interfaces [13]. Using  $D_{\rm it} = C_{\rm mis} \times \Delta V_{\rm th}/e$ , the density of the trap states in the MIS diode was estimated to be  $2.2 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ , significantly lower compared to that of the Al<sub>2</sub>O<sub>3</sub> MOS diode. In addition, frequency dependent conductance analysis was performed in the frequency range of 1 kHz to 1 MHz to evaluate the trap states time constant  $(\tau_{\rm T})$  and trap states density  $(D_{\rm T})$ . The conductance technique for determination of the trap states in MIS capacitors is generally accepted as the most accurate method [14, 15]. Figure 7 shows the plot of parallel conductance  $(G_{\rm P}/\omega)$  as a function of the radial frequency for the selected gate voltages near threshold voltage  $(V_{th})$  for the MIS diode with 7 nm *in situ*  $SiN_x$ . By fitting the experimental

**Figure 5** Gate-pulsed/DC output (left) and transfer (right) characteristics of a 7 nm *in situ* SiN<sub>x</sub>/AlN/GaN MISHEMT with  $L_G = L_{GS} = L_{GD} = 1 \mu m$ .

**Figure 7** Frequency dependent parallel conductance as a function of radial frequency for selected gate voltages near  $V_{\text{th}}$ .

data, the values of  $D_{\rm T}$  and  $\tau_{\rm T}$  were extracted to be  $D_{\rm T} = 1.9-3.4 \times 10^{12} \,{\rm cm}^{-2} \,{\rm eV}^{-1}$  and  $\tau_{\rm T} = 0.8-17 \,\mu{\rm s}$ . The trap states density of this *in situ* SiN<sub>x</sub>/AlN/GaN MISHEMT indicates the feasibility of *in situ* SiN<sub>x</sub> as gate dielectric for ultra-thin-barrier AlN/GaN MISHEMTs. Further, the  $D_{\rm T}$  can be improved by choosing the optimal *in situ* SiN<sub>x</sub> growth conditions, such as temperature, pressure, and the ratio between silane and ammonia.

**4 Conclusions** In summary, the use of *in situ*  $SiN_x$  grown by MOCVD as the gate dielectric for ultra-thinbarrier AlN/GaN MISHEMTs on Si substrates has been described and discussed. The achieved results demonstrate that the *in situ*  $SiN_x$  layer can effectively suppress the leakage current and protect the AlN surface.

Acknowledgements This work was supported in part by the Research Grants Council (RGC) theme-based research scheme (TRS) of the Hong Kong Special Administrative Region Government under grant T23-612/12-R. Support of the Nanofabrication Facilities (NFF) of HKUST was also acknowledged.

## References

- T. Huang, X. Zhu, and K. M. Lau, IEEE Electron Device Lett. 33, 1123–1125 (2012).

- [2] T. Zimmermann, D. Deen, Y. Cao, J. Simon, P. Fay, D. Jena, and H. Grace Xing, IEEE Electron Device Lett. 29, 661–664 (2008).

- [3] Y. Cao, K. Wang, A. Orlov, H. Xing, and D. Jena, Appl. Phys. Lett. 92, 152112 (2008).

- [4] F. Medjdoub, M. Zegaoui, D. Ducatteau, N. Rolland, and P. A. Rolland, IEEE Electron Device Lett. 32, 874–876 (2011).

- [5] S. Taking, D. MacFarlane, and E. Wasige, IEEE Trans. Electron Devices 58, 1418–1424 (2011).

- [6] T. Huang, X. Zhu, K. M. Wong, and K. M. Lau, IEEE Electron Device Lett. 33, 212–214 (2012).

- [7] M. Higashiwaki, T. Mimura, and T. Matsui, IEEE Electron Device Lett. **27**, 719–721 (2006).

- [8] D. Deen, D. Storm, D. Meyer, D. S. Katzer, R. Bass, S. Binari, and T. Gougousi, Phys. Status Solidi C 8, 2420–2423 (2011).

- [9] D. A. Deen, S. C. Binari, D. F. Storm, D. S. Katzer, J. A. Roussos, J. C. Hackley, and T. Gougousi, Electron. Lett. 45, 423–424 (2009).

- [10] E. Cho, S. Seo, C. Jin, D. Pavlidis, G. Fu, J. Tuerck, and W. Jaegermann, J. Vac. Sci. Technol. B 27, 2079–2083 (2009).

- [11] M. Higashiwaki, Z. Chen, R. Chu, Y. Pei, S. Keller, U. K. Mishra, N. Hirose, T. Matsui, and T. Mimura, Appl. Phys. Lett. 94, 053513 (2009).

- [12] P. Yi, S. Rajan, M. Higashiwaki, C. Zhen, S. P. DenBaars, and U. K. Mishra, IEEE Electron Device Lett. **30**, 313–315. (2009).

- [13] M. Fagerlind, F. Allerstam, E. O. Sveinbjornsson, N. Rorsman, A. Kakanakova-Georgieva, A. Lundskog, U. Forsberg, and E. Janzen, J. Appl. Phys. **108**, 014508 (2010).

- [14] J. J. Freedsman, T. Kubo, S. L. Selvaraj, and T. Egawa, Jpn. J. Appl. Phys. 50, 04DF03 (02011).

- [15] P. Kordos, R. Stoklas, D. Gregusova, and J. Novak, Appl. Phys. Lett. 94, 223512 (2009).